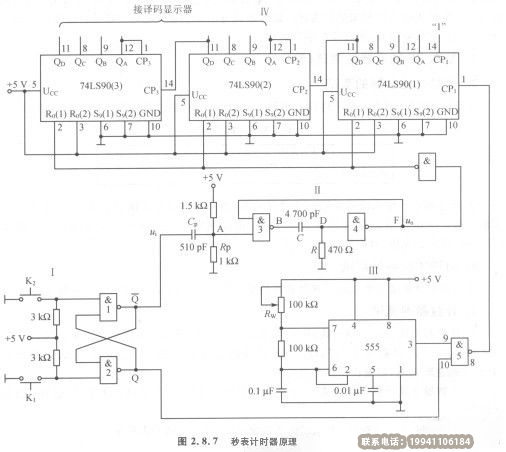

秒表计时器的基本原理由图2.8.7所显示,现将该图分四个一部分开展功能设计。

1)计时器的起动和终止电源电路 ET1103G

计时器的起停电源电路由基础RS触发器构成。

图2.8.7单元I为集成化与非门组成的基础RS触发器。基础RS触发器的2个键入端由旋钮开关K.和K:操纵。按压旋钮开关K,门1接地装置,Q=O,它是校准情况;再按压旋钮开关K门2接地装置,Q=l,门5打开,为起动计数器做准备。Q由1变O,送出去负单脉冲,起动单稳态触发器工作中。

2)计数器清零电源电路

计数器清零电源电路,由图2.8.7中所显示的单元Ⅱ的求微分型单稳态触发器构成。

由基础RS触发器Q端出示的负单脉冲,做为单稳态触发器键入数据信号,使单稳态触发器輸出负单脉冲,根据非门加到计数器的消除端,为计数器出示清零数据信号。

3)时钟产生器

图2.8.7所显示的单元Ⅲ是555电路组成的多谐振荡器,它是一种特性不错的时钟源。调整电阻器Rw,使輸出端3得到 頻率为50 Hz\'的矩形框波数据信号,该差分信号根据门5做为记数单脉冲加在计数器1的记数键入端CPi。

4)记数显示信息电源电路

图2.8.7所显示的单元Ⅳ是二、五、十进制加法器74LS90组成电子秒表的记数单元。在其中计数器2连接成五进制方式,对頻率为50

Hz的时钟单脉冲开展五分频,做为计数器3的时钟键入。计数器2及计数器3连接成8421码十进制方式。其輸出端与译码器显示信息单元的相对键入端联接,可显示信息0. 1~0.9 s、1~9.9 s记时。

18069884716 18069884716

18069884716 18069884716 杭州市滨江区浦沿工业园园区中路(至仁街)22号泰衡大楼2号楼3楼

杭州市滨江区浦沿工业园园区中路(至仁街)22号泰衡大楼2号楼3楼 led-gift@gxleds.net

led-gift@gxleds.net